publications

Our work is appeared on journal/conference proceedeings of variety of research area including circuits (IEEE JSSC, IEEE ISSCC, IEEE A-SSCC), DA/architecture (IEEE Design & Test, ASP-DAC, ACM/IEEE MICRO), mobile (IEEE Pervasive Computing, ACM SenSys), HCI (ACM CHI, ACM UIST, ACM TEI).

Only selected publications are displayed below. For all the publications, you can see Google Scholar or researchmap.

2024

2023

-

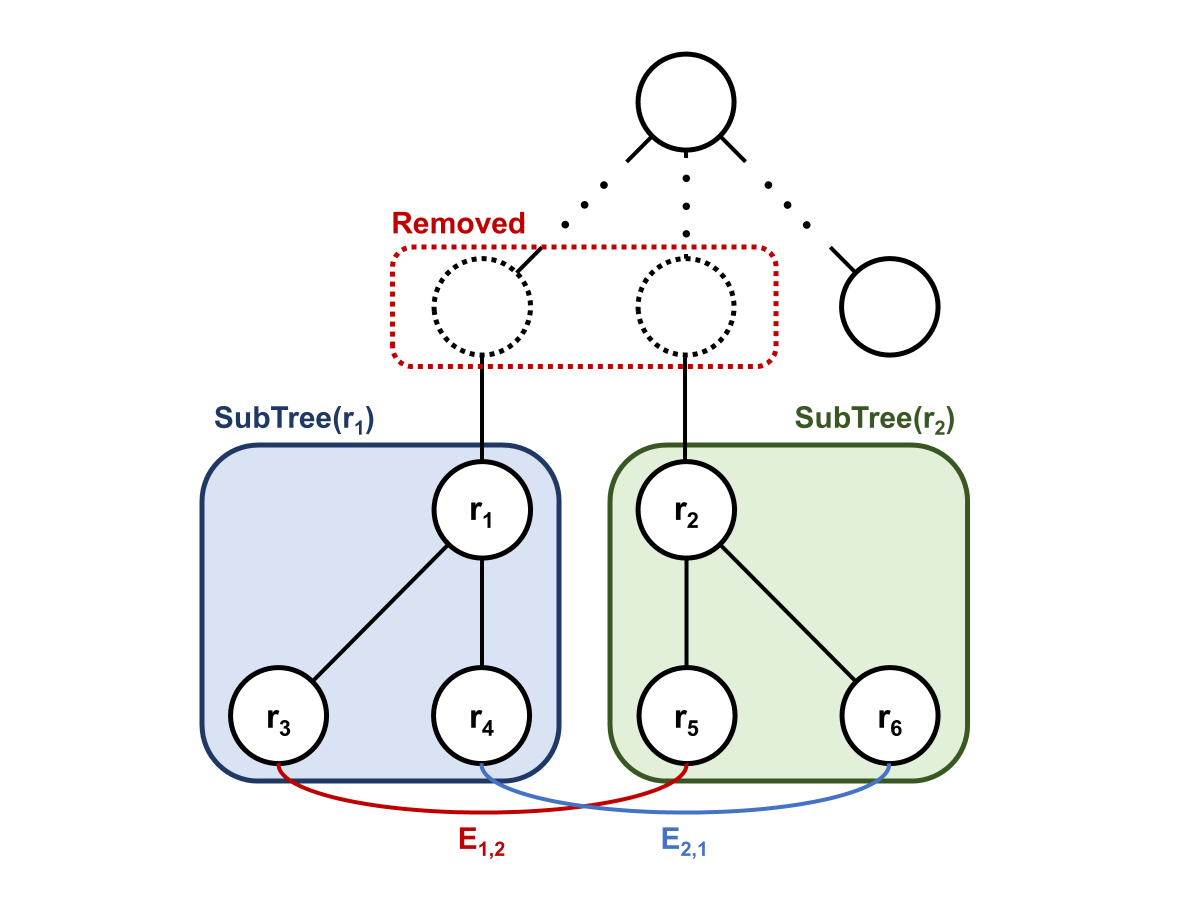

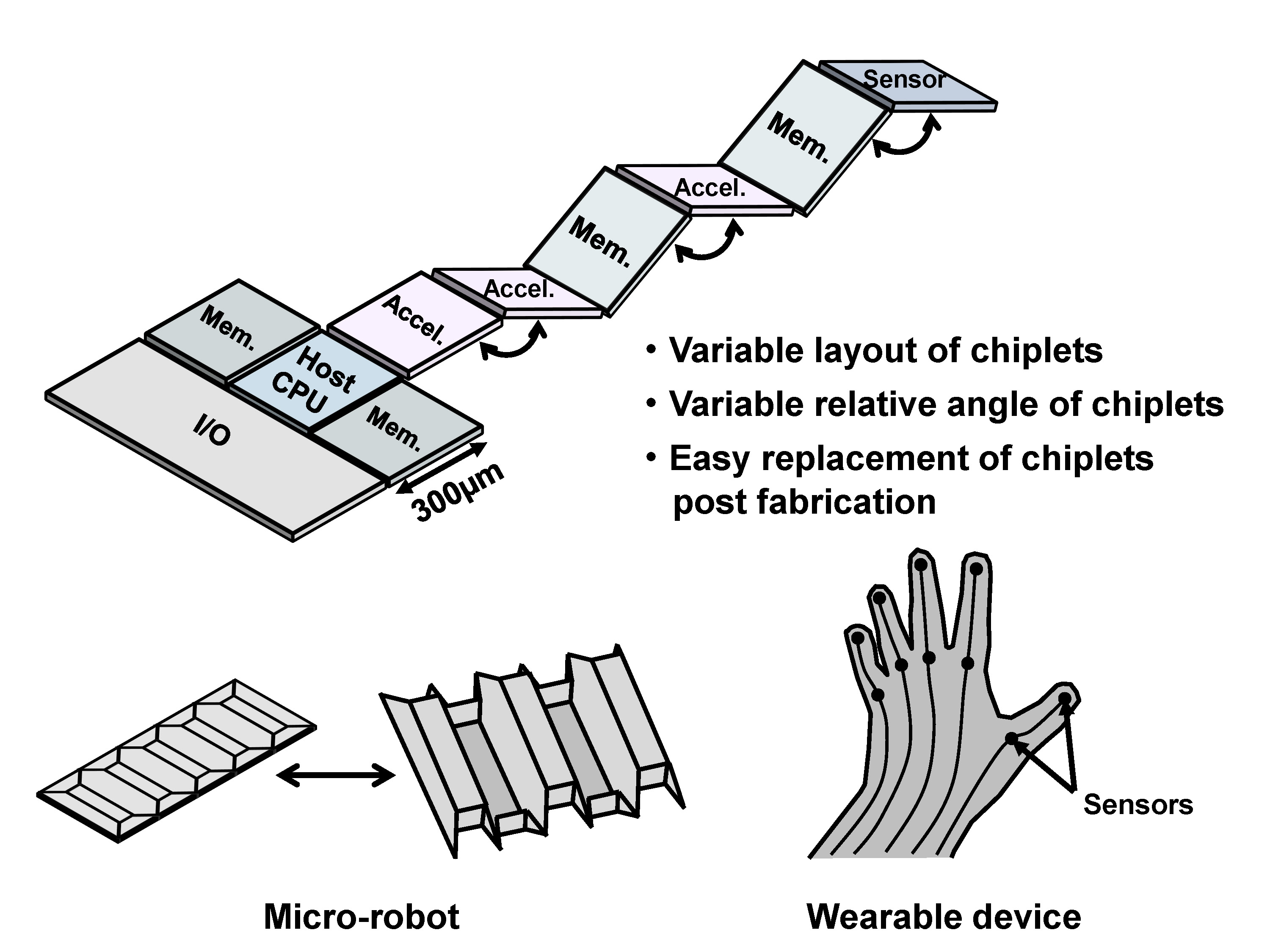

Dynamically Reconfigurable Network Protocol for Shape-Changeable Computer SystemIEEE Design & Test, Dec 2023

Dynamically Reconfigurable Network Protocol for Shape-Changeable Computer SystemIEEE Design & Test, Dec 2023

2021

-

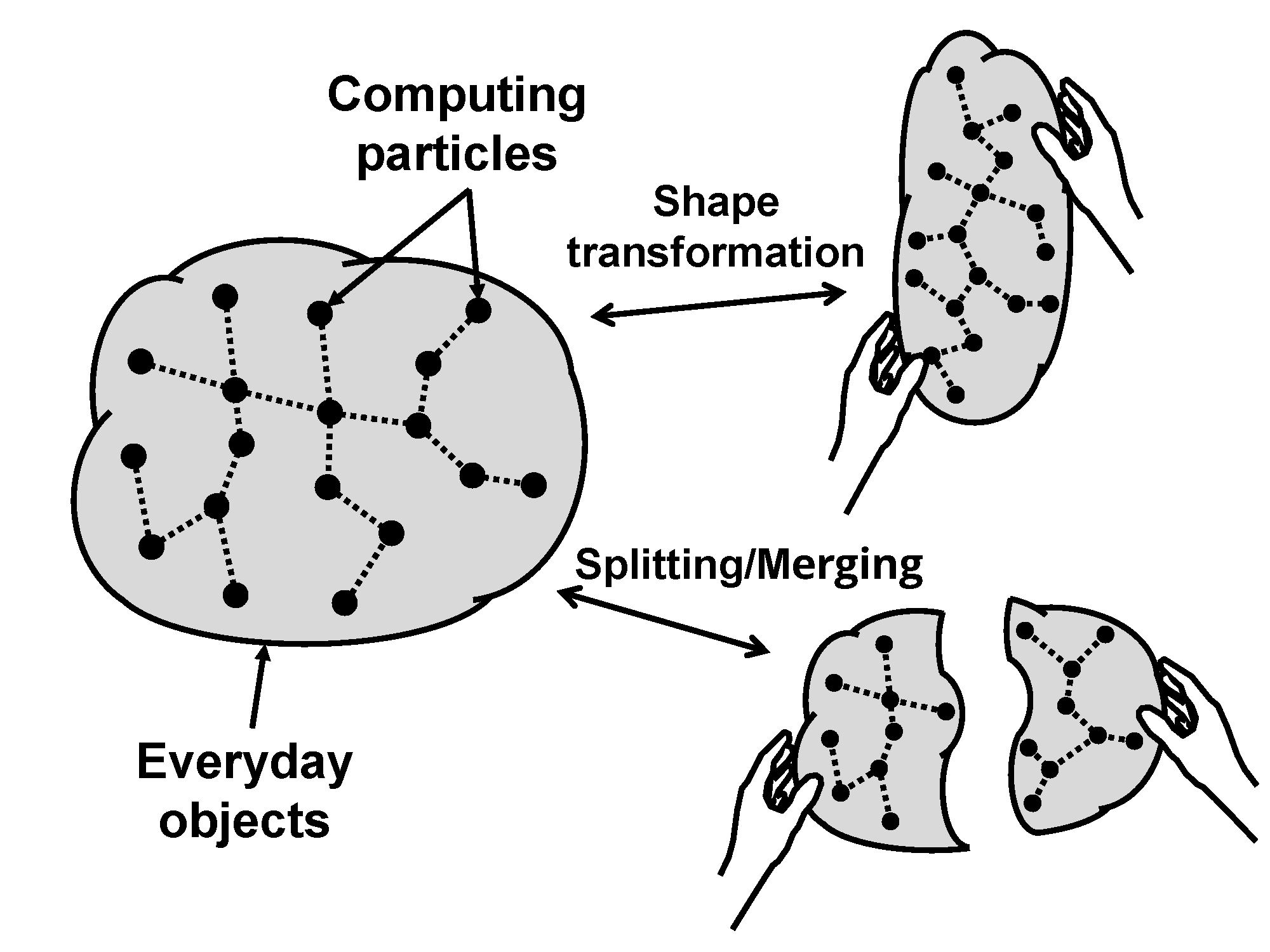

Toward Wirelessly Cooperated Shape-Changing Computing ParticlesIEEE Pervasive Computing, Jul 2021

Toward Wirelessly Cooperated Shape-Changing Computing ParticlesIEEE Pervasive Computing, Jul 2021

2020

-

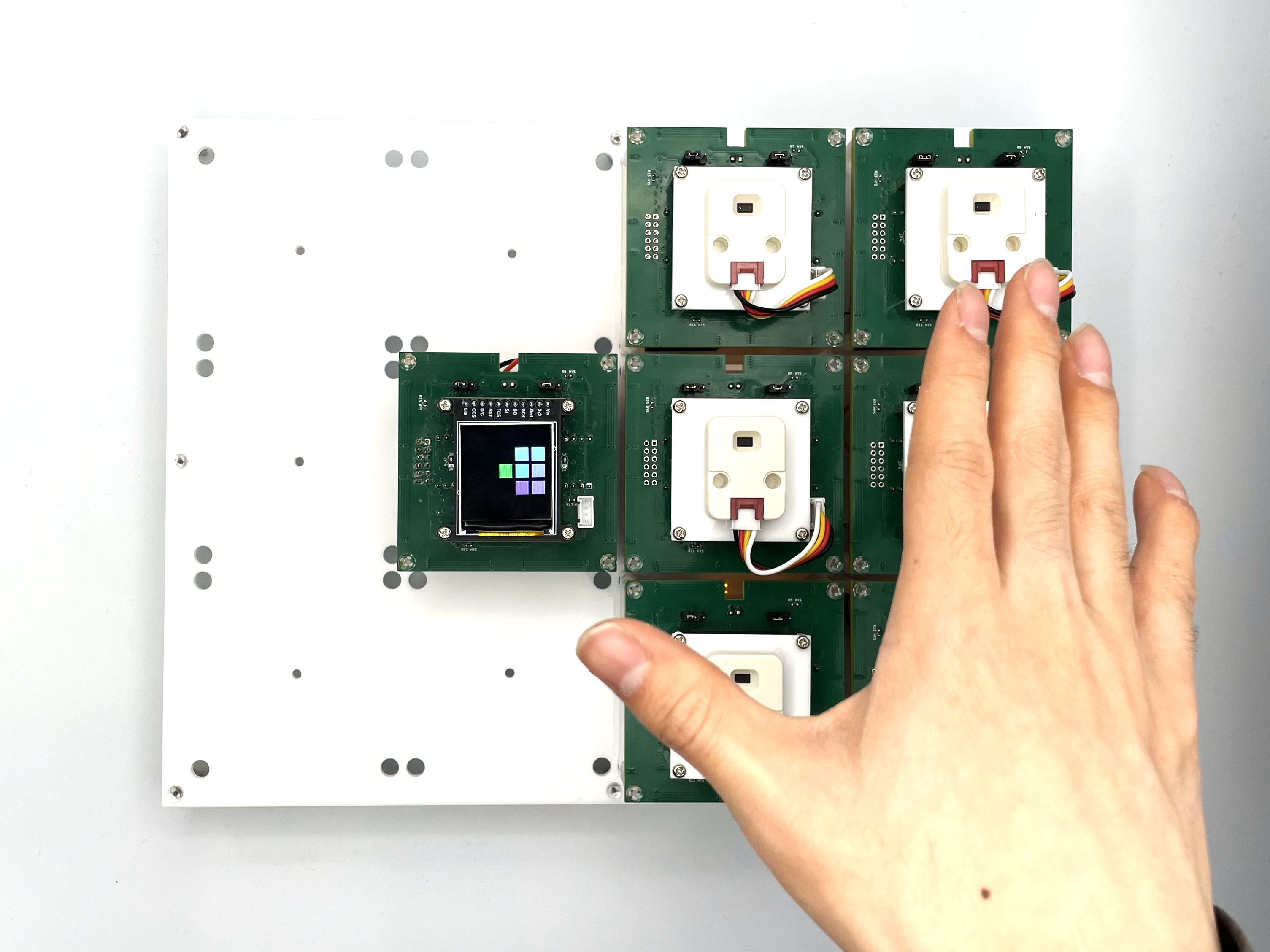

Design of Shape-Changeable Chiplet-Based Computers Using an Inductively Coupled Wireless Bus InterfaceIn IEEE International Conference on Computer Design (ICCD) , Oct 2020

Design of Shape-Changeable Chiplet-Based Computers Using an Inductively Coupled Wireless Bus InterfaceIn IEEE International Conference on Computer Design (ICCD) , Oct 2020

2019

-

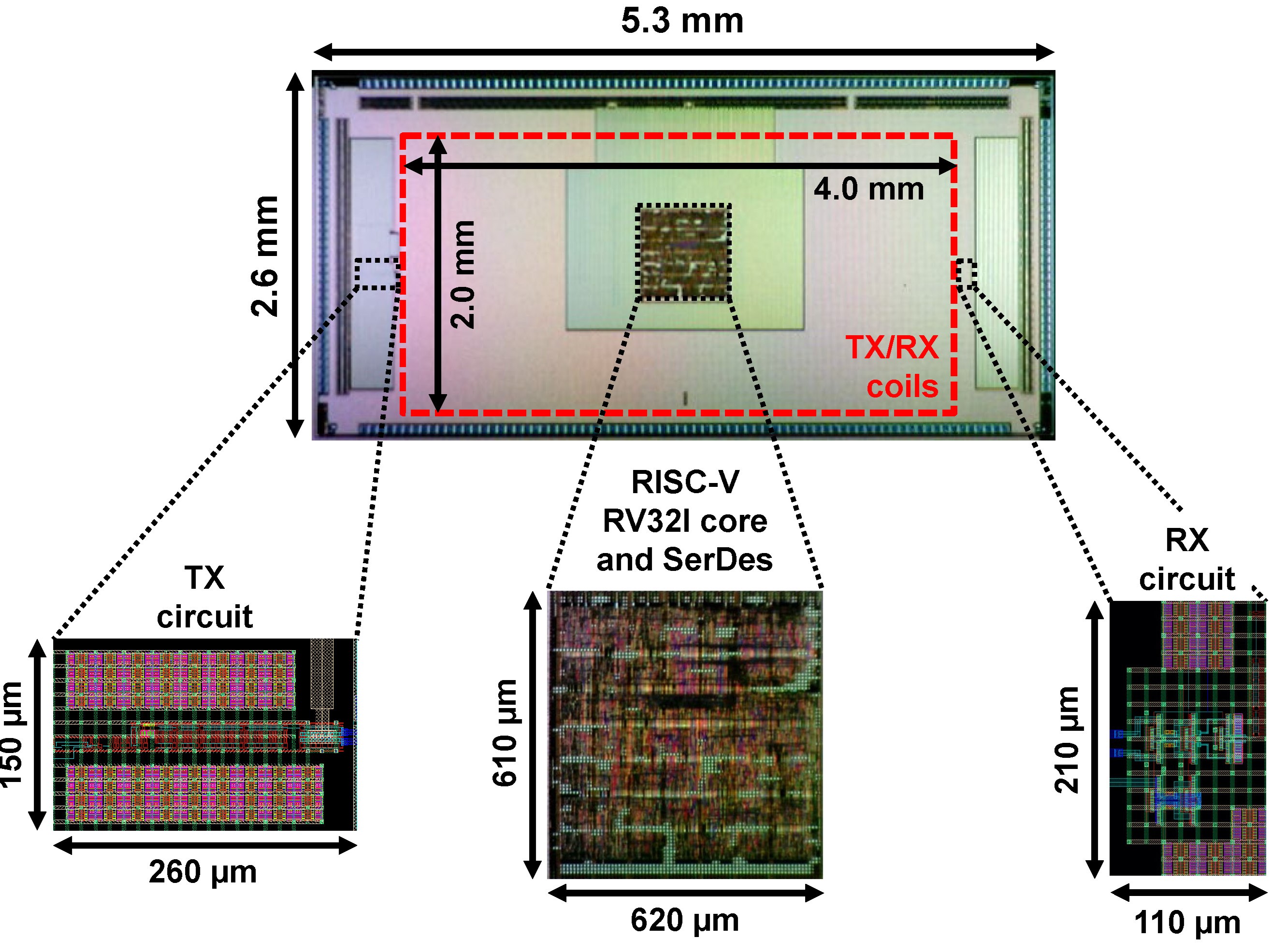

WiXI: An Inter-Chip Wireless Bus Interface for Shape-Changeable Chiplet-Based ComputersIn IEEE International Conference on Computer Design (ICCD) , Nov 2019

WiXI: An Inter-Chip Wireless Bus Interface for Shape-Changeable Chiplet-Based ComputersIn IEEE International Conference on Computer Design (ICCD) , Nov 2019